|

|

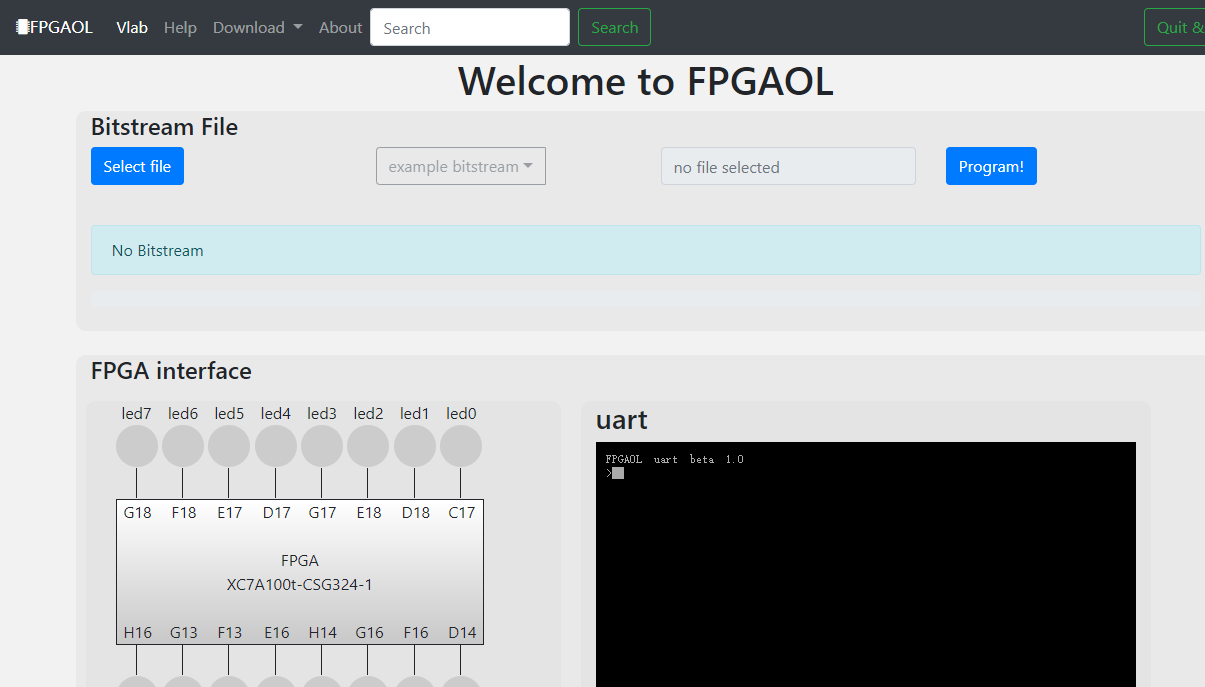

@@ -20,19 +20,19 @@ Press **select file** button to select your bitstream file.

|

|

|

|

|

|

|

|

|

|

|

|

-Then, press **Program** button to upload and program your bistream file. It will take approximately 10 Secs to upload and program.

|

|

|

+Then, press **Program** button to upload and program your bitstream file. It will take approximately 10 Secs to upload and program.

|

|

|

|

|

|

|

|

|

|

|

|

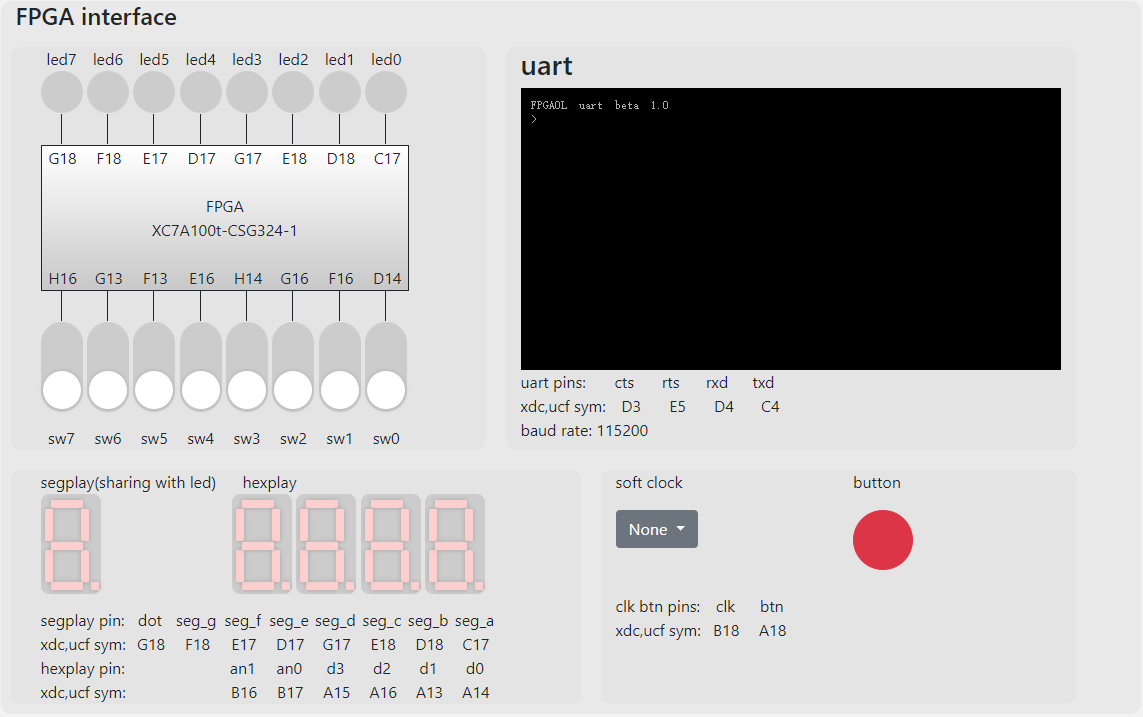

### use human interface

|

|

|

|

|

|

-After the bistream file is successfully uploaded and programmed, you can gain access to human interface to test your design. The behavor depends on your design.

|

|

|

+After the bistream file is successfully uploaded and programmed, you can gain access to FPGA interface to test your design. The behavor depends on your design.

|

|

|

|

|

|

|

|

|

|

|

|

### use waveform

|

|

|

|

|

|

-Sample-based waveform chart is provided.

|

|

|

+Sample-based waveform chart is provided.

|

|

|

|

|

|

|

|

|

|